**EE 215D**

## Midterm Exam Spring 2003

Name: Solutions

Time Limit: 2 Hours

Open Book, Open Notes

|  |   |   | * |

|--|---|---|---|

|  | 1 |   |   |

|  |   |   |   |

|  |   |   | * |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   | • |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

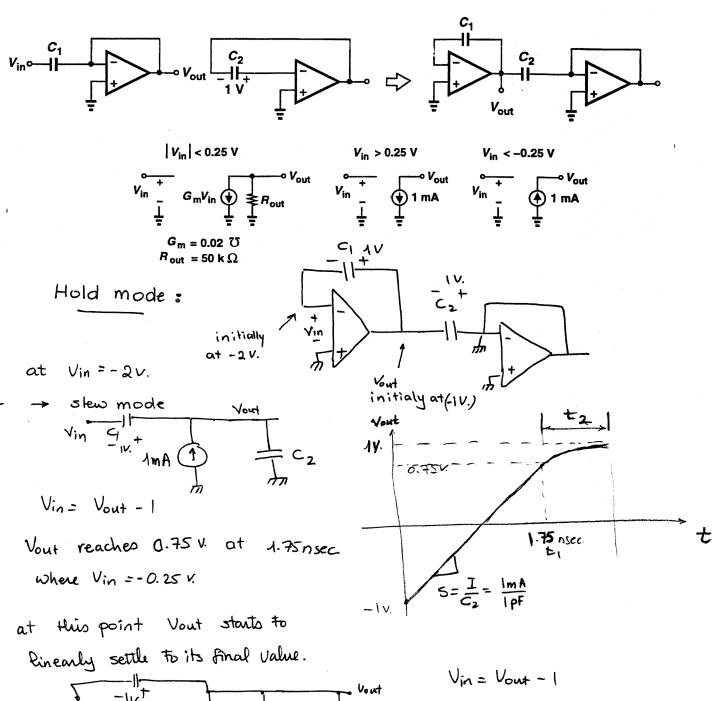

1. Two unity-gain samplers appear in a pipeline as shown below. When the first stage is in the acquisition mode, the second is in the hold mode and vice versa. Suppose  $V_{in}=1$  V and model the op amp as shown below. With the initial condition shown in the second stage, determine the time it takes  $V_{out}$  to reach within 0.1% of its final value. You can assume the second op amp creates a good virtual ground at its inverting input in this mode. Sketch the waveform for  $V_{out}$  as the first stage goes from sampling to hold. Assume  $C_1 = C_2 = 1$  pF.

$$V_{out}(0) = 0.75 v.$$

$$-Gm (Vowt-1) = \frac{Vout}{Rout} + C_2 \frac{dVout}{dt}$$

$$= \frac{1}{Rout} Vout + Gm = C_2 \frac{dVout}{dt}$$

$$Gm = 0.02$$

$Rout = 50 k$

$C_{2} = 1PF$

$$C_2 \frac{dVout}{dt} + (G_m + \frac{1}{Rout}) Vout = + G_m.1$$

$$V_{0ut}(0) = 0.75$$

Solving Eqn (1)

$$\frac{G_{m+1}}{G_{m+1}} + \left(\frac{G_{m}}{G_{m+1}} + 0.75\right) e^{\frac{t}{C_{2}} \cdot \left(G_{m+1}\right)}$$

$$\frac{U_{out}(v)}{G_{m+1}} + \left(\frac{G_{m}}{G_{m+1}} + 0.75\right) e^{\frac{t}{C_{2}} \cdot \left(G_{m+1}\right)}$$

$$\frac{V_{out}(w)}{V_{out}(w)} = \frac{G_{m}}{G_{m+1}} = 0.999 \quad V.$$

:. The time it takes Vout to reach 0.1% of its final value =

$$t_1 + t_2 = 1.75 + 0.2758 = 2.0258$$

nsec

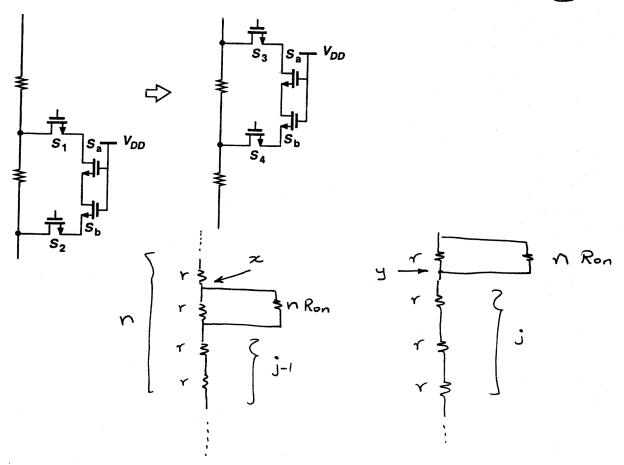

2. A resistor-ladder DAC incorporates MOS switches as resistors in a secondary ladder. The diagram below shows how the secondary ladder slides up and down along the primary one. Is this DAC monotonic for any value of the MOS on-resistance,  $R_{on}$ ? Why or why not? Use detailed analysis to support your claim.

x, y are the same point but in two diff. situations:

$$V_{x} = \frac{(j-1) r + r //(n Ron)}{(n-1) r + r //(n Ron)}$$

,  $V_{y} = \frac{jr}{(n-1) r + r // n Ron}$

to be monotanic - Vx < Vy

This DAC is unconditionally Monitoric for any value of Ron.

| 4 |  |  |     |  |

|---|--|--|-----|--|

|   |  |  | 1   |  |

|   |  |  | , , |  |

|   |  |  |     |  |

|   |  |  |     |  |

|   |  |  |     |  |

- 3. Consider the two nominally-equal capacitors shown below. The initial condition at node X is zero.

- (a) Assuming each capacitor can be expressed as  $C = C_0(1 + \alpha_1 V)$ , determine the value of  $V_X$  after the transitions shown in the figure occur.

- (b) Repeat part (a) if  $C = C_0(1 + \alpha_1 V + \alpha_2 V^2)$ .

(a)

$$C_{1} \quad C_{2}$$

$$V_{0} \quad C_{1} \quad C_{2}$$

$$V_{0} \quad C_{1} \quad V_{X} \quad C_{2} \quad -V_{0}$$

$$C = C_{0} \left( 1 + \alpha_{1} V \right)$$

From conservation of change

$$\rightarrow$$

$q_1 = q_2$

$$\begin{array}{ccc}

V_0 - V_X & V_X - (-V_0) \\

\vdots & \int C_1 dV_1 &= \int C_2 dV_2 \\

\vdots & C_0 \left( (V_0 - V_X) + \frac{\alpha_1}{2} (V_0 - V_X)^2 \right) &= C_0 \left( (V_X + V_0) + \frac{\alpha_1}{2} (V_0 + V_X)^2 \right)

\end{array}$$

$$2(\alpha_1 V_0 + 1) V_X = 0 \qquad \longrightarrow \qquad \boxed{V_X = 0}$$

similarly,

:.

$$V_{x} \left( 1 + \alpha_{1} V_{0} + \alpha_{2} V_{0}^{2} + \frac{\alpha_{2}}{3} V_{x}^{2} \right) = 0$$

$$v_{x}^{2} = 0$$

or  $V_{x}^{2} = -\frac{3}{\alpha_{2}} \left( 1 + \alpha_{1} V_{0} + \alpha_{2} V_{0}^{2} \right)$

|  |   |   | 4 |

|--|---|---|---|

|  | · | • | • |

|  |   |   | ž |

|  |   |   | • |

|  | · |   | • |

|  |   |   | f |

|  |   |   | • |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   | • |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

|  |   |   |   |

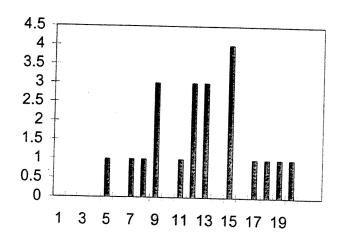

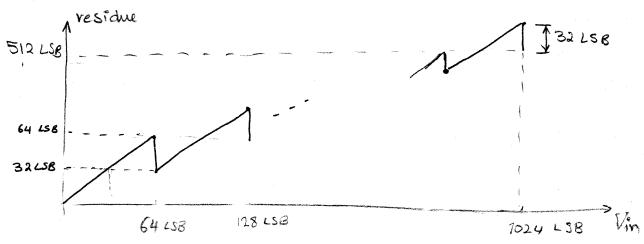

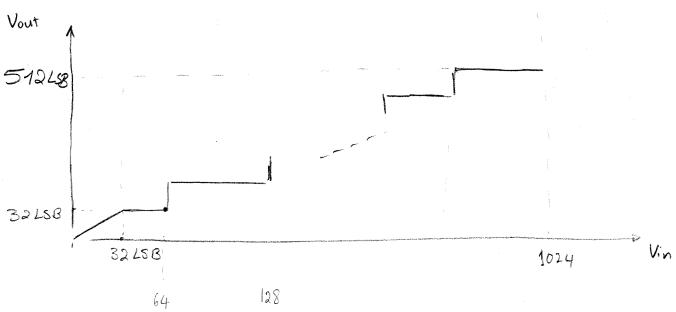

- 4. Consider a 10-bit two-step ADC similar to that in Homework #4. Each stage resolves 5 bits and the subtractor has a voltage gain of unity. The reference voltage for the first-stage ladder is nominally equal to 1024 LSB and that for the second-stage ladder equal to 32 LSB.

- (a) Suppose the reference voltage for the first-stage ladder is accidentally chosen to be 2048 LSB but that for the second stage is still equal to 32 LSB. Plot the residue and the overall input-output characteristic and determine critical errors. Assume DAC output varies between 0 and 1024 LSB,

- (b) Suppose the reference voltage for the second-stage ladder is accidentally chosen to be 64 LSB but that for the first stage is still equal to 1024 LSB. Plot the residue and the overall input-output characteristic and determine critical errors.

(a) If the reference voltage of 1st stage is 2048 LSB

DNL = 32 LSB

(b) ref. voltage of the 2nd stage ladder = 64 LSB residue 32 LSB 1024 32 4 Vout 1024178 64 LSB

1024

DNL= 1 LS8

₩ 2LSB 32LSB

32LSB