EE 215D

## Midterm Exam Spring 2012

Name: Solutions

- 1. 10

- 2.10

- 3. /0

- 4. 10

Total: 40

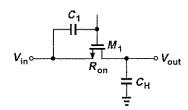

- 1. Consider the bootstrapped sampling circuit shown below, where the body of  $M_1$  is tied to ground and the rest of the bootstrap network is not shown.

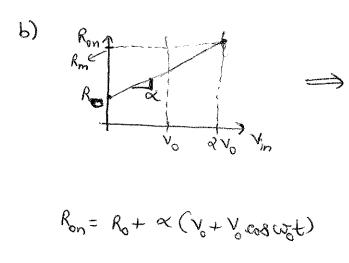

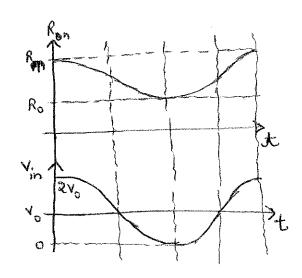

- (a) If body effect is not neglected, sketch the on-resistance of  $M_1$  as a function of  $V_{in}$ . You need not write equations.

- (b) Approximating the characteristic in (a) by a straight line passing through its end points, sketch  $R_{on}$  as a function of time. Assume  $V_{in}(t) = V_0 \cos \omega_0 t + V_0$ .

- (c) Calculate the second harmonic amplitude at the output arising from phase distortion. Assume that the phase shift is much less than 1 radian.

Ron =

$$\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$$

$\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$   $\frac{1}{kW(V_{GS} - V_{tho} - 8(T\phi + V_{SB} - T\phi))}$

Voit =  $\frac{1}{2}$   $\frac{1}{$

2nd Harmonic Amplitude -> [ 1 vox wo CH

where  $\alpha$  is given by  $R_{on} = R_o + \alpha V_{in}$

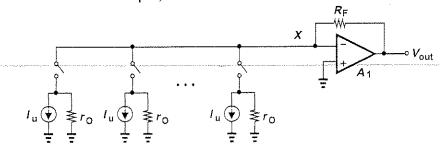

- 2. A segmented current-steering DAC consists of N current sources and is followed by a transimpedance amplifier as shown below. Assume the op amp has a gain of  $A_1$  but is otherwise ideal.

- (a) Estimate the INL at node X. (1pt)

- (b) Estimate the INL at the output. (3pt)

(a)

$$INL_{X}(n) = V_{X}(n) - V_{X}, ideal(n) = \frac{I_{X}V_{0}R_{F}^{2}}{VR_{F} + (A_{1}+1)V_{0}} \cdot \frac{N(n-N)}{NR_{F} + (A_{1}+1)V_{0}}$$

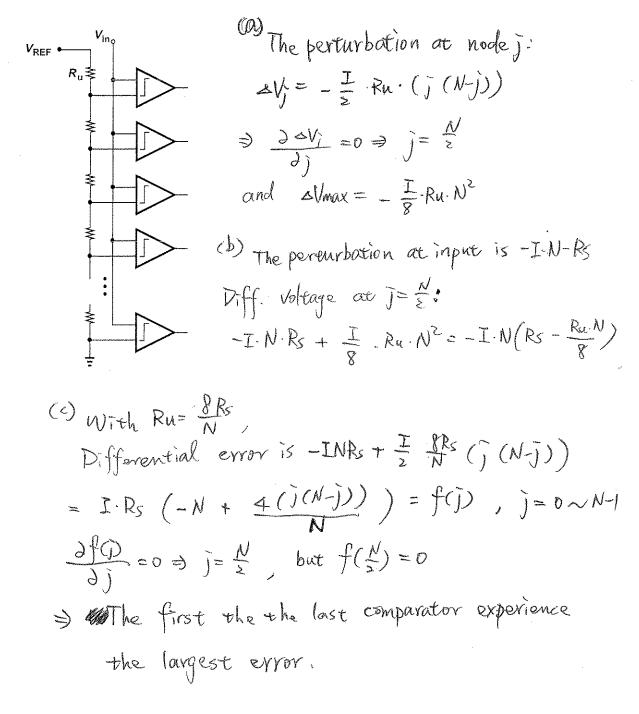

- 3. Consider the flash ADC shown below. Assume  $V_{in}$  is provided by an ideal voltage source.

- (a) If the kickback noise currents of all comparators are equal and denoted by I(t), determine the largest perturbation voltage on the ladder. Assume I(t) is small.

- (b) Now assume that  $V_{in}$  is provided through a source impedance of  $R_S$ . Compute the differential voltage experienced by the comparator tied to  $V_{REF}/2$ . Assume that the kickback noise currents drawn by the two inputs of each comparator are equal.

- (c) Suppose we choose the total ladder resistance equal to  $8R_S$ . Which comparator does now experience the largest differential error?

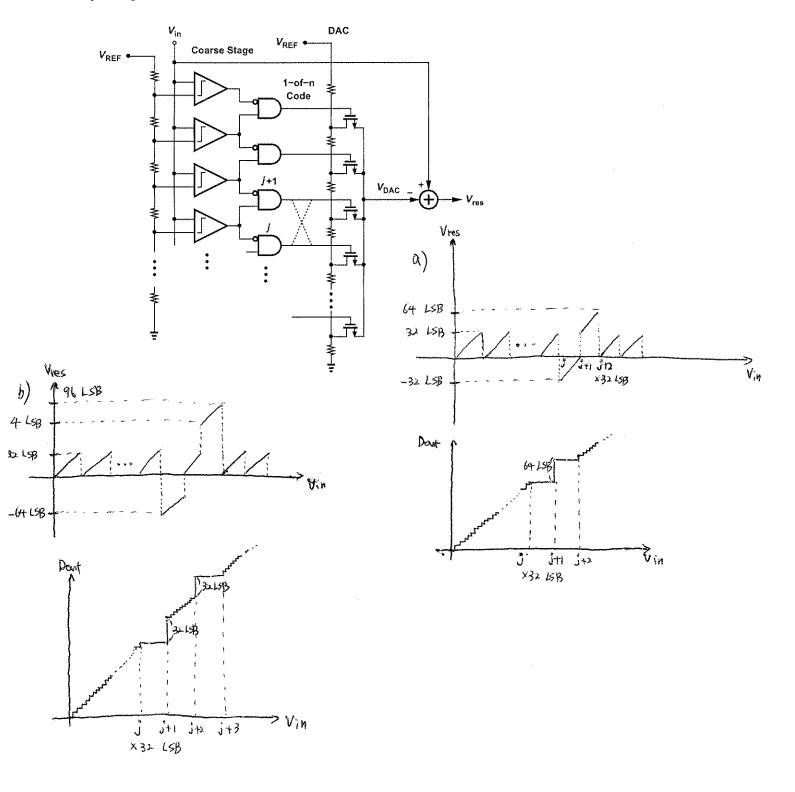

- 4. Consider the 10-bit two-step ADC studied in Homework 4, where each stage resolves 5 bits. Assume that the DAC employs a resistor ladder as shown below. Analyze the following two cases independently.

- (a) Suppose the outputs of NAND gates j and j+1 are accidentally swapped. Construct the residue plot and the input/output characteristic.

- (a) Suppose the outputs of NAND gates j and j + 2 are accidentally swapped. Construct the residue plot and the input/output characteristic.