#### **PLLs and Synthesizers**

Behzad Razavi Electrical Engineering Department University of California, Los Angeles

### Outline

- Phase Detector

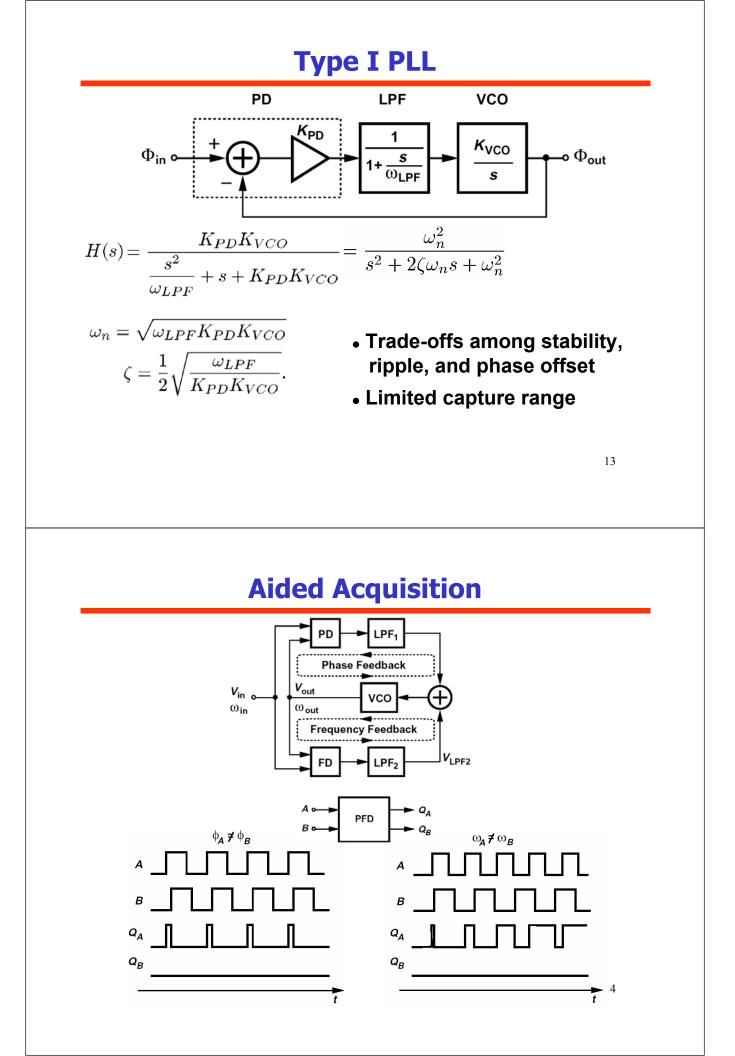

- Type I and II PLLs

- PLL Design Procedure

- Synthesizer Architectures

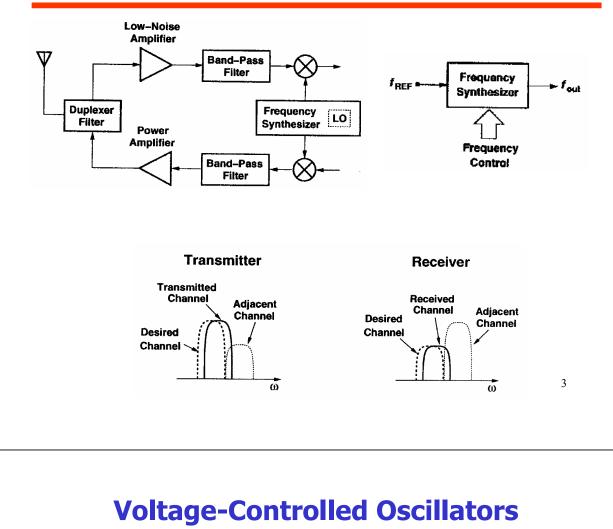

# **The Need for RF Synthesis**

- Center Frequency

- Tuning Range:

- Band of Interest

- PVT Variations

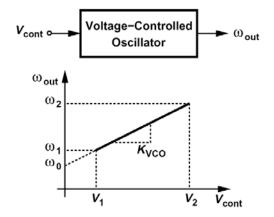

- Gain (Sensitivity)

$K_{VCO} \ge \frac{\omega_2 - \omega_1}{V_2 - V_1}$

- Supply Rejection

- Tuning Linearity

- Intrinsic Jitter

- Output Amplitude

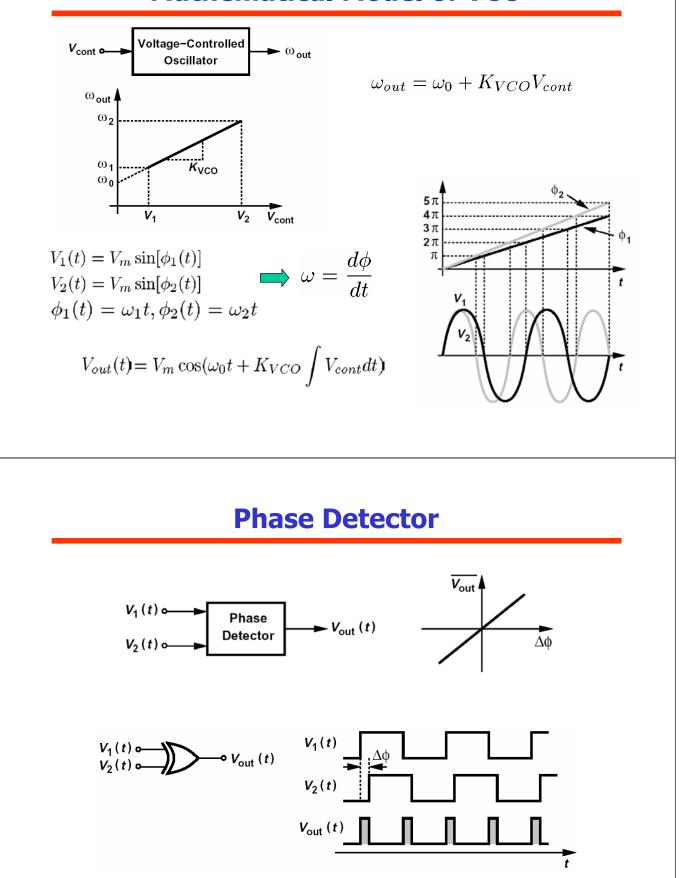

## **Mathematical Model of VCO**

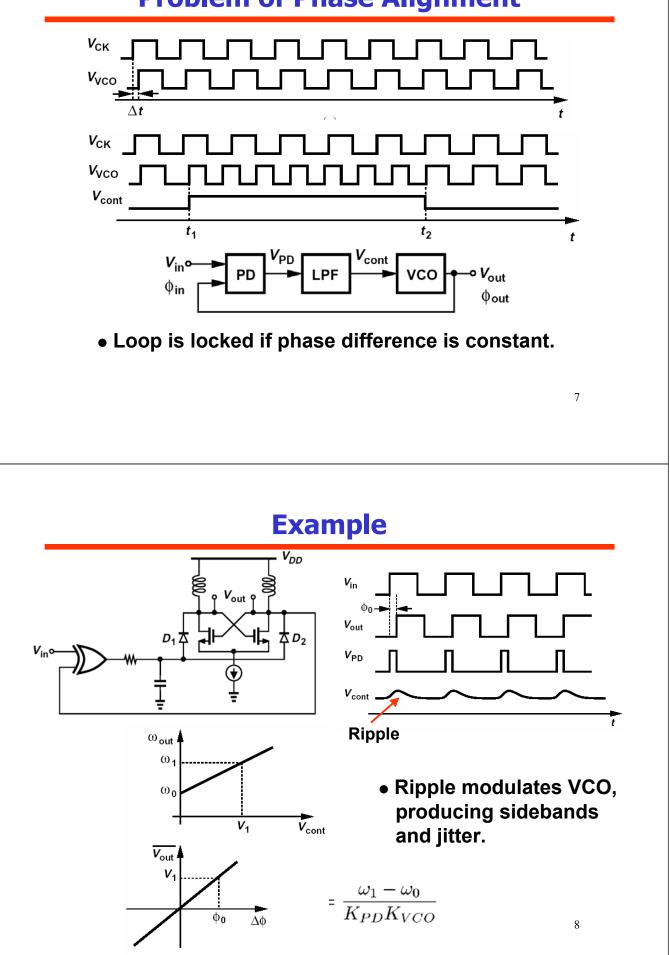

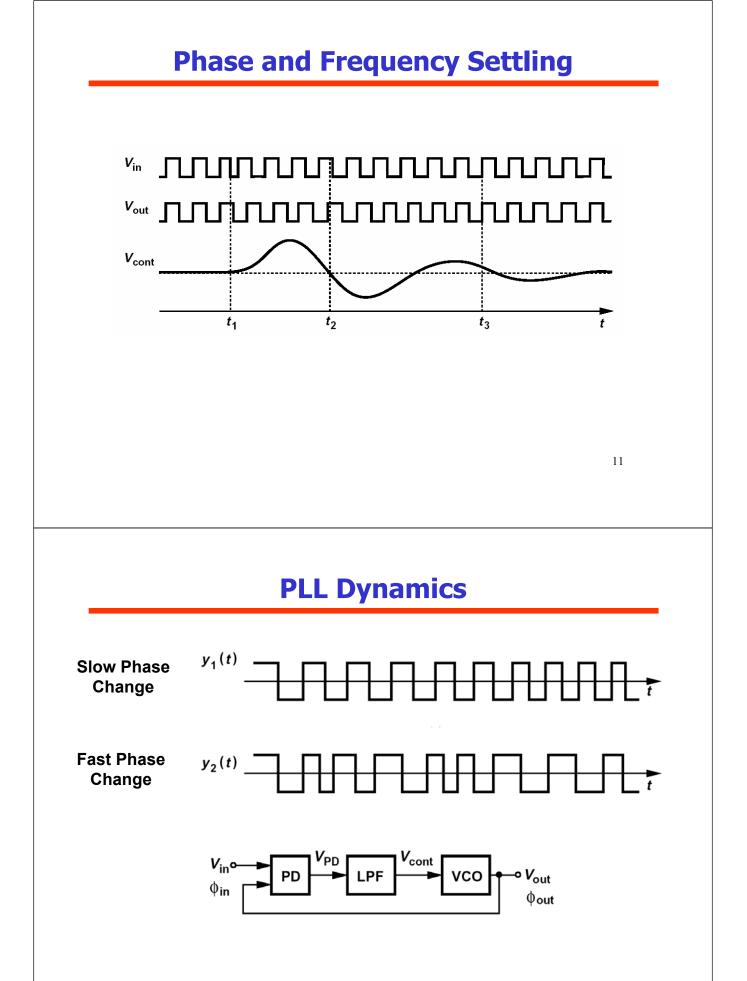

### **Problem of Phase Alignment**

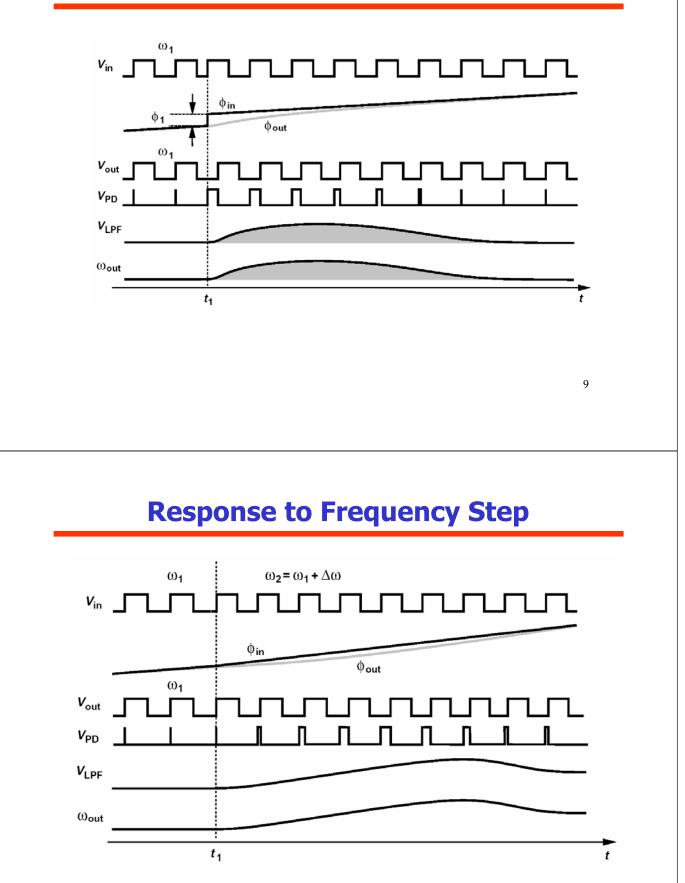

#### **Response to Phase Step**

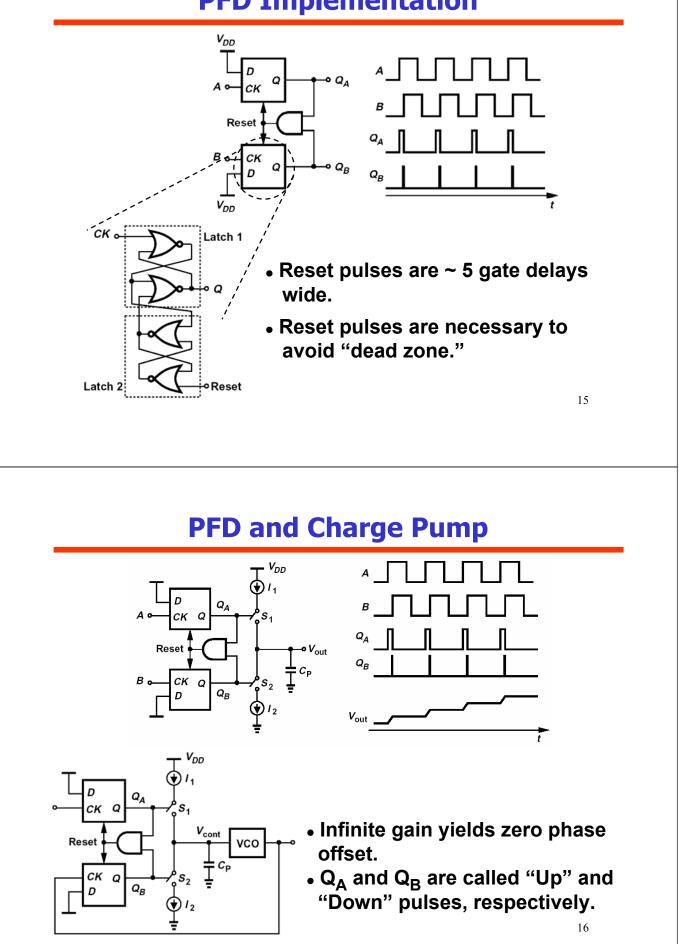

# **PFD Implementation**

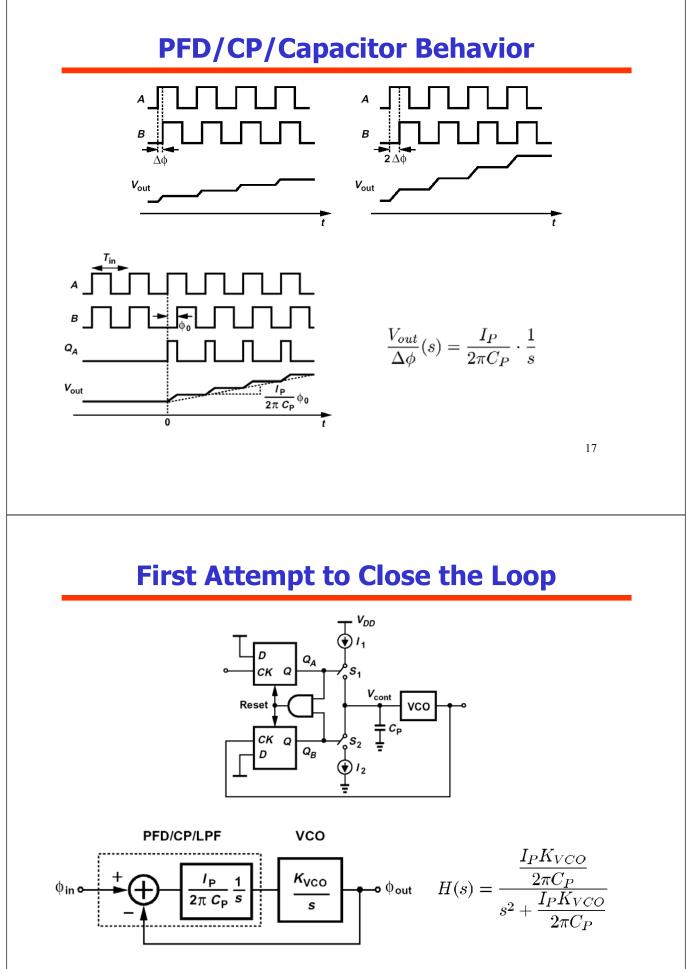

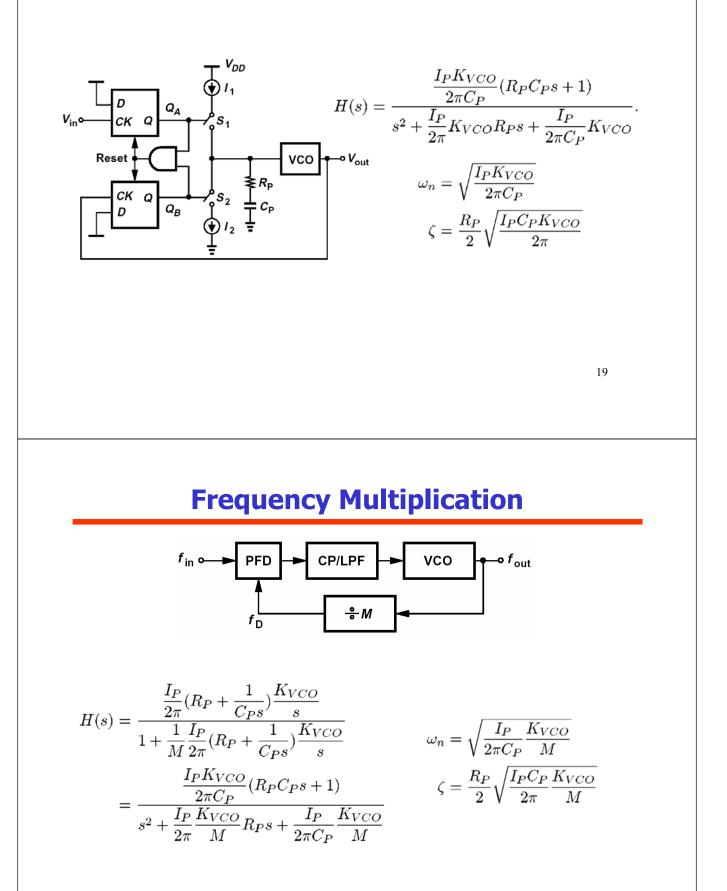

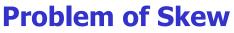

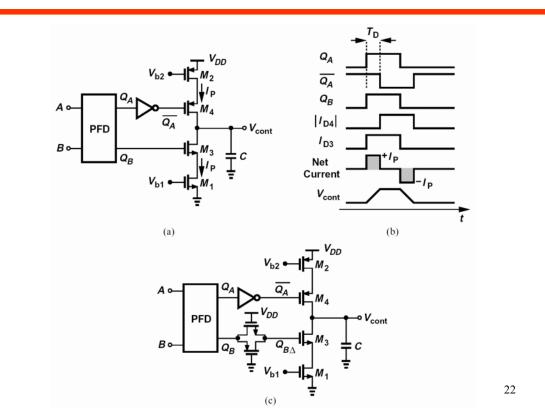

#### Type II (Charge-Pump) PLL

### **PFD/CP Nonidealities**

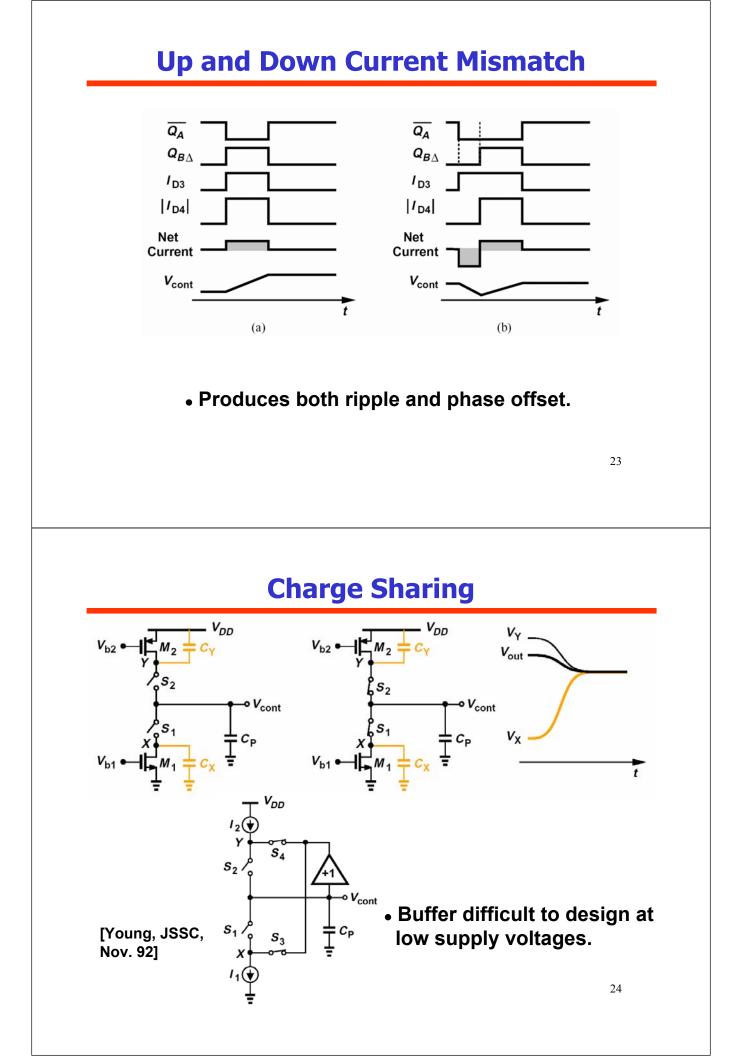

- Skew between Up and Down

Pulses

- Mismatch between Up and Down Currents

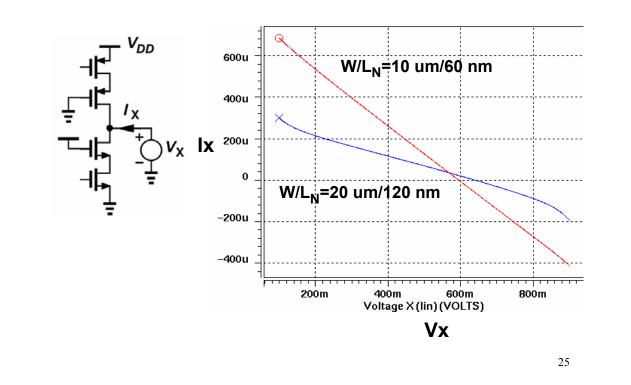

- Charge Sharing

- Channel-Length Modulation

- Charge Injection Mismatch

### **Channel-Length Modulation**

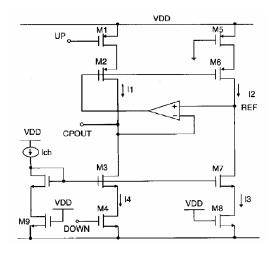

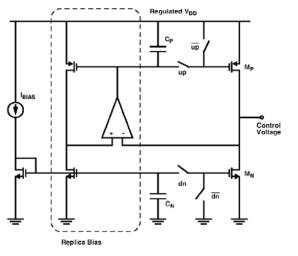

#### **Reduction of Channel-Length Modulation**

[Lee, Elec. Let., Nov. 00]

[Terrovitis, ISSCC04]

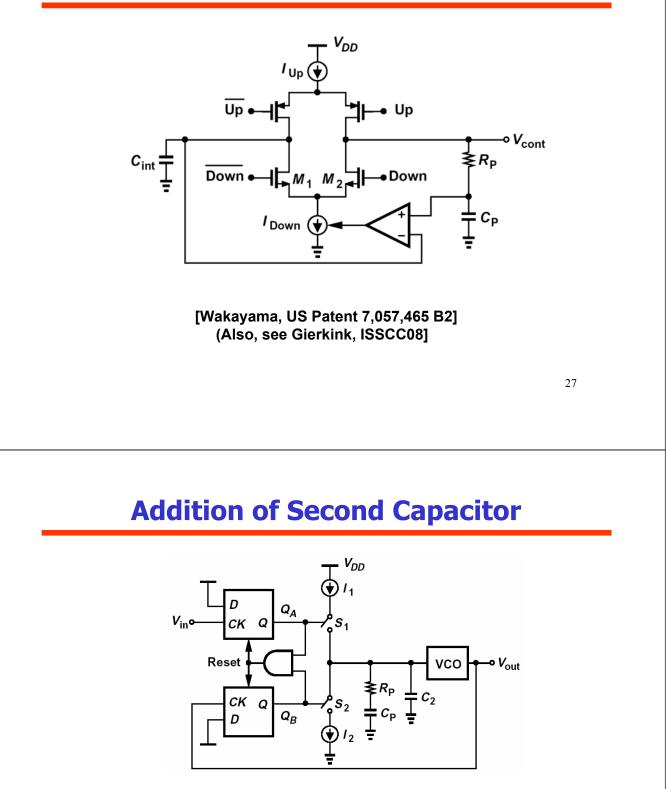

## **Reduction of Both Mismatches**

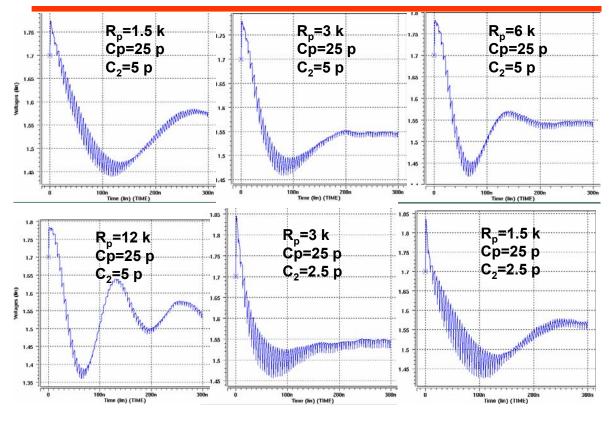

- C<sub>2</sub> can reach 0.2Cp with little degradation in settling behavior.

- But imposes an upper bound on Rp.

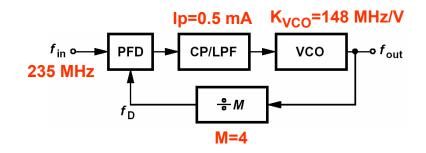

### **PLL Design Procedure**

- Design VCO for frequency range of interest and obtain  $\ensuremath{\mathsf{K}_{\text{VCO}}}\xspace$

- Set the "loop bandwidth" to one-tenth of input frequency:

$$\omega_{-3dB}^2 = \left[ (2\zeta^2 + 1) + \sqrt{(2\zeta^2 + 1)^2 + 1} \right] \omega_n^2$$

(Loop BW ~ 2.5 $\omega_n$  for  $\zeta$  = 1.)

- Select a charge pump current (tens of microamps to some milliamps).

- Set the damping factor to 1 and compute Rp and Cp.  $\sqrt{I_P K_{VCO}}$

$$\zeta = \frac{R_P}{2} \sqrt{\frac{I_P C_P}{M}} \frac{K_{VCO}}{M}$$

29

#### **Charge Pump Design**

- Select W/L of current sources for an overdrive of about 50-100 mV.

- Choose L such that mismatch due to channellength modulation remains below 10-20%.

- Choose switch dimensions for a headroom consumption of 20-30 mV.

- If mismatch due to channel-length modulation results in excessive jitter or sidebands:

- (a) Increase C<sub>2</sub> and Cp (BW goes down).

- (b) Use one of the circuit techniques to reduce effect of channel-length modulation.

**Simulated Behavior**

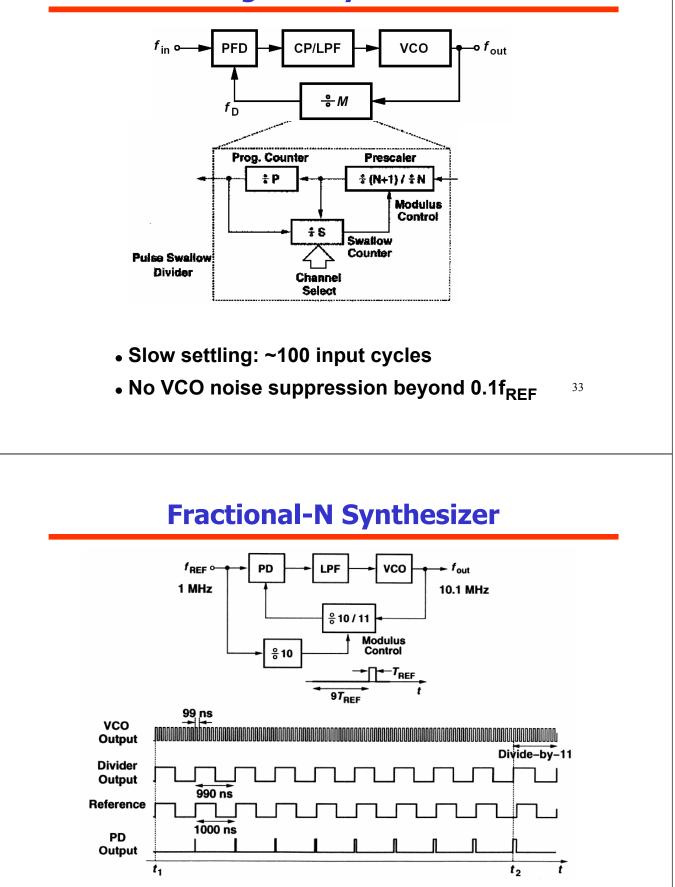

### **Integer-N Synthesizer**

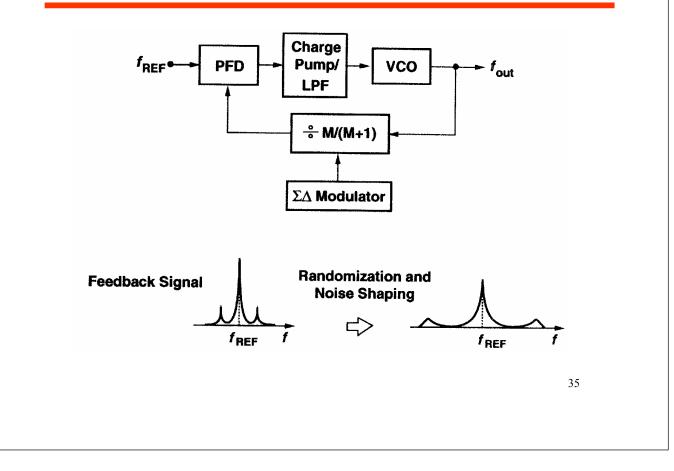

## $\Sigma \Delta \text{ Fractional-N Synthesizer}$